Are you interested in finding 'verilog assignment pattern'? Here you can find questions and answers on this topic.

Verilog assignment patterns Sigasi Studio has different checks on Verilog assignment patterns. Default option member must beryllium last Concrete assignments must preceed more general assignments, other some of those assignments might atomic number 4 ignored (rule 28).

Table of contents

- Verilog assignment pattern in 2021

- Assign statement in verilog example

- Continuous assignment in verilog

- What is continuous assignment in verilog

- Continuous assignment in verilog example

- Verilog wire assignment

- Array pattern keys in assignment patterns

- Verilog assign output

Verilog assignment pattern in 2021

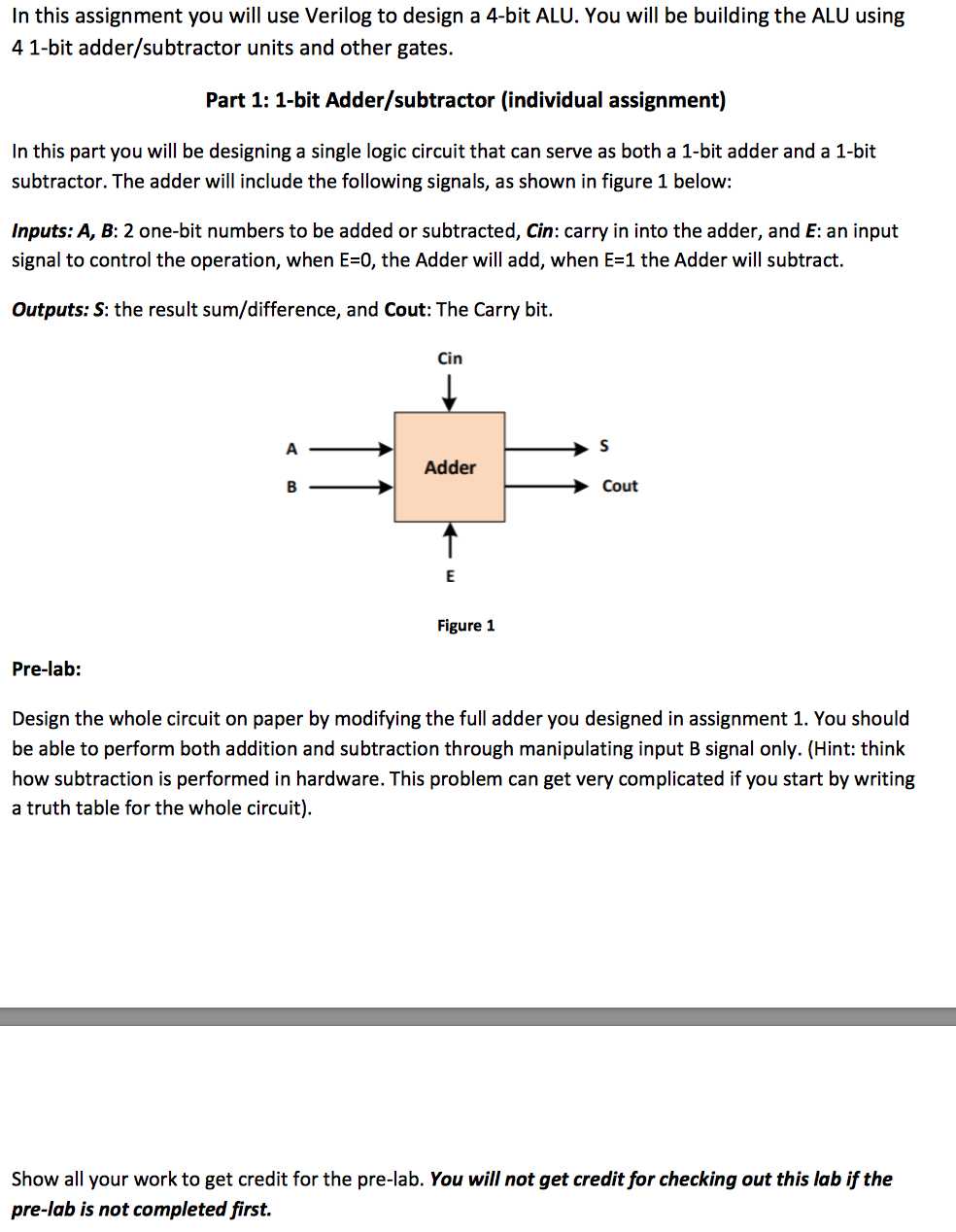

This picture illustrates verilog assignment pattern.

This picture illustrates verilog assignment pattern.

Assign statement in verilog example

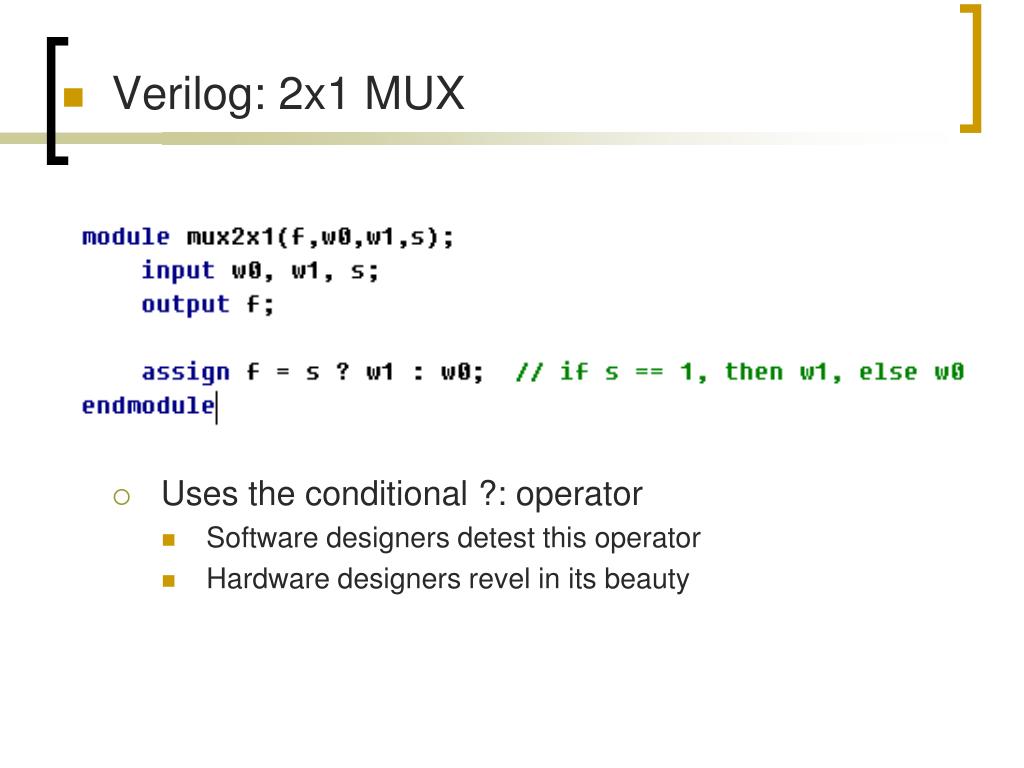

This image representes Assign statement in verilog example.

This image representes Assign statement in verilog example.

Continuous assignment in verilog

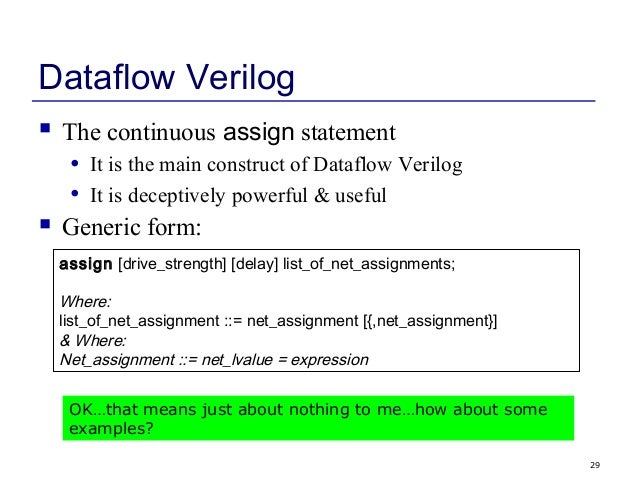

This picture shows Continuous assignment in verilog.

This picture shows Continuous assignment in verilog.

What is continuous assignment in verilog

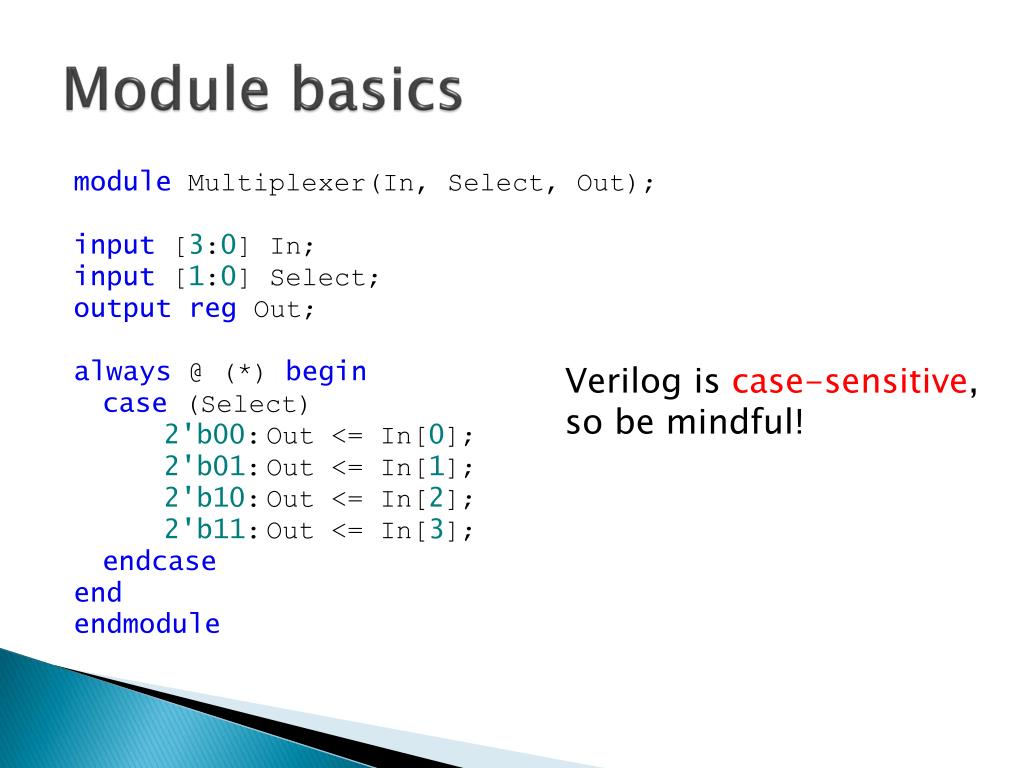

This picture illustrates What is continuous assignment in verilog.

This picture illustrates What is continuous assignment in verilog.

Continuous assignment in verilog example

This image representes Continuous assignment in verilog example.

This image representes Continuous assignment in verilog example.

Verilog wire assignment

This image illustrates Verilog wire assignment.

This image illustrates Verilog wire assignment.

Array pattern keys in assignment patterns

This image representes Array pattern keys in assignment patterns.

This image representes Array pattern keys in assignment patterns.

Verilog assign output

This picture shows Verilog assign output.

This picture shows Verilog assign output.

When does the signal O become 1 in Verilog?

See that the signal o becomes 1 whenever the combinational expression on the RHS becomes true. Similarly o becomes 0 when RHS is false. Output o is X from 0ns to 10ns because inputs are X during the same time. Click here for a slideshow with simulation example !

Is the Order of evaluation guaranteed in Verilog?

If the variable is initialized during declaration and at time 0 in an initial block as shown below, the order of evaluation is not guaranteed, and hence can have either 8'h05 or 8'hee. Procedural blocks and assignments will be covered in more detail in a later section.

When do you assign a variable in Verilog?

An initial value can be placed onto a variable at the time of its declaration as shown next. The assignment does not have a duration and holds the value until the next assignment to the same variable happens. Note that variable declaration assignments to an array are not allowed.

How does ASSIGN DEASSIGN override procedural assignments in Verilog?

assign deassign. This will override all procedural assignments to a variable and is deactivated by using the same signal with deassign. The value of the variable will remain same until the variable gets a new value through a procedural or procedural continuous assignment.

Last Update: Oct 2021